# Extreme Power-Constrained Integrated Circuit Design

by

Mingoo Seok

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 2011

Doctoral Committee:

Professor Dennis Michael Sylvester, Chair Professor David Blaauw Associate Professor Scott Malhke Assistant Professor David Dale Wentzloff

to my family

## ACKNOWLEDGEMENTS

I have been extremely fortunate to interact with and learn from a great group of both professors and fellow students during my graduate study. This work would have been impossible without their contributions. My advisor, Dennis Sylvester and practically another advisor, David Blaauw have guided and inspired me throughout the last five year of graduate study. Jae-sun Seo and Youngmin Kim were also tremendously helpful to me when I first started the doctoral progam.

I have been particularly lucky to have great collaborators in all of my projects. Scott Hanson, Yu-Shiang Lin and I worked together to design Phoenix Processor in Chapter II under the guidance of Dennis Sylvester and David Blaauw. Yoonmyung Lee, Zhiyoong Foo, Daeyeon Kim and Rach Liu also contributed to the project's success. Scott Hanson also offered valuable discussions in the study on power gating switches in Chapter IV. Jae-sun Seo and Scott Hanson helped the read-only-memory project in Chapter V. Gyouho Kim contributed to design and test of 2-Transistor voltage references in Chapter VI. Finally, Dongsuk Jeon and I closely worked together to create the world-record energy-efficient Fast Fourier Transform core in Chapter VII.

Not directly involved in the same projects, Bo Zhai, Carlos Tokunaga, Sanjay Pant, Gregory Chen, Michael Wieckowski, Vineeth Veetil, David Fick, Inhee Lee, Matthew Fojtik, Mohammad Hassan, Eric Karl, Youngmin Kim, Prashant Singh, Dongmin Yoon, Yejoong Kim, Jerry Kao, Wei-Shiang Ma, Bharan Girdidhar, Brian Cline, Cheng Zhou, and Sudhir Satpahy have been great discussion partners in the field of VLSI research. I also thank Youngmin Park, Sangwook Han, Daeyoung Lee, Seunghyun Oh, Jaeyoung Joshua Kang, Jungkap Park, Dongjin Lee, Sangwon Seo, Razi Haque, Myungchul Kim, Hyo Gyuem Rhew, Changwook Min, David Lee, Youngjun Park, Junsun Park, Gwang-hyeon Baek, Youngjoon Song, Younghyun Shim, Jungkook Kim, Geonwook Yoo, Kyunghoon Lee, Seunghyun Lee, Juseop Lee, Sunghyun Cho, Hyungil Chae, Junseok Heo, Byungsoo Kim, Jooseuk Kim, Cheolwon Alexander Min, Seun Park, Deahyun Yoon, Daeyon Jung, Yoojin Choi and Jongwoo Lee for the discussions on the topics outside digital design. I would also like to thank the Korea Foundation of Advanced Studies and the Rackham Graduate School for funding my fellowship for total three years.

Last but not the least, I thank my family (father, mother, wife, partents in law, sister, sister's husband, sisters and a brother in law) and friends for their unconditional supports.

# TABLE OF CONTENTS

| DEDICATIO   | Ν                                                              | ii |

|-------------|----------------------------------------------------------------|----|

| ACKNOWLE    | DGEMENTS i                                                     | ii |

| LIST OF FIG | URES                                                           | х  |

| LIST OF TAI | BLES                                                           | v  |

| LIST OF AB  | BREVIATIONS                                                    | /i |

| ABSTRACT    | xvi                                                            | ii |

| CHAPTER     |                                                                |    |

| I. Intro    | $\mathbf{duction}$                                             | 1  |

| 1.1         | Emerging Sensing Applications                                  | 1  |

| 1.2         | Challenges of Achieving Cubic Millimeter Scale Sensing Systems | 3  |

| 1.3         | Reducing Power Consumption in ICs                              | 4  |

|             | 1.3.1 Power Consumption in Modern IC design                    | 4  |

|             | 1.3.2 Ultra Low Voltage Operation                              | 5  |

| 1.4         |                                                                | 7  |

|             |                                                                | 7  |

|             | 1.4.2 Designing Ultra Low Power Analog Building Blocks         | 8  |

|             | 1.4.3 Improving Performance, Delay Variability and En-         |    |

|             |                                                                | 9  |

|             | 1.4.4 Contribution Summary                                     | 1  |

| 1.5         |                                                                | 3  |

| II. Phoe    | nix Processor: 35pW Standby and 226nW Active Power             |    |

| Senso       | r Platform                                                     | 4  |

| 2.1         |                                                                | 4  |

| 2.2         |                                                                | 6  |

| 2.3         | System Overview                                                | 6  |

|         | 2.4        | System-level Optimization including Technology Selection     | 18       |

|---------|------------|--------------------------------------------------------------|----------|

|         | 2.5        | Power Gating Under Relaxed Performance Constraints           | 22       |

|         | 2.6        | CPU and Instruction Set Design for Standby Mode              | 24       |

|         | 2.7        | DMEM Compression for Standby Mode                            | 26       |

|         | 2.8        | Ultra-Low Standby Power Memory Design                        | 30       |

|         | 2.9        | Test Chip Overview                                           | 34       |

|         | 2.10       | Measured Results                                             | 35       |

|         |            | 2.10.1 Power and Performance Results                         | 35       |

|         |            | 2.10.2 Power Gating Results                                  | 37       |

|         |            | 2.10.3 Memory Results                                        | 37       |

|         | 2.11       | Summary                                                      | 41       |

| III. Te | echn       | ology Selections for Ultra Low Voltage Design                | 42       |

|         | 3.1        | Motivation and Previous Work                                 | 42       |

|         | 3.2        | Contribution                                                 | 44       |

|         | 3.3        | Ultra Low Voltage Application Spaces                         | 44       |

|         | 3.4        | Basic Optimal Technology Selection for Minimum Energy        | 46       |

|         |            | 3.4.1 Modeling Logic and SRAM for Energy Comparison          | 46       |

|         |            | 3.4.2 Technology Choice for Minimum Energy                   | 47       |

|         | 3.5        | Impact of Standby Leakage Reduction                          | 48       |

|         |            | 3.5.1 Leakage Reduction Methods in Ultra Low Voltage         | 40       |

|         |            | Regimes                                                      | 49<br>50 |

|         | າເ         | 3.5.2 Technology Choice with Leakage Reduction Schemes       | 50<br>51 |

|         | 3.6        | Effect of Logic and SRAM Ratio on Technology Selection       | 51<br>52 |

|         | 3.7        | Variability and Technology Selection                         | 53<br>54 |

|         |            | 3.7.1 Impact of Operating Point on Variability               | 54       |

|         | <b>n</b> 0 | 3.7.2 Technology Selection for Min Variability $\ldots$      | 55       |

|         | 3.8        | Summary                                                      | 58       |

| IV. Po  | ower       | Gating Switch Design for Ultra Low Voltage Operations        | 60       |

|         | 4.1        | Motivation and Previous Work                                 | 60       |

|         | 4.2        | Contributions                                                | 61       |

|         | 4.3        | Impact of Sleep Energy on Total Energy Consumption           | 62       |

|         | 4.4        | The Effects of Cutoff Structures on Total Energy Consumption | 64       |

|         |            | 4.4.1 Theoretical Power Gating Switch                        | 65       |

|         |            | 4.4.2 Practical Power Gating Switch                          | 67       |

|         | 4.5        | Strategy of Design Power Gating Switches                     | 71       |

|         |            | 4.5.1 PGS Design Strategies in Ultra Low $V_{DD}$ Regimes .  | 71       |

|         |            | 4.5.2 Comparisons of the Optimization Methods                | 75       |

|         |            | 4.5.3 Case Study Using a Fabricated Microprocessor           | 77       |

|         | 4.6        | Feasibility of Minimal-Sized PGSs                            | 78       |

|         | 4.7        | Beyond Basic PGSs                                            | 80       |

|         | 4.8        | Summary                                                      | 82       |

| V. Robus    | st Ultra Low Voltage ROM Design                         | 83  |

|-------------|---------------------------------------------------------|-----|

| 5.1         | Motivation and Previous Work                            | 83  |

| 5.2         | Contributions                                           | 84  |

| 5.3         | Dynamic NAND Read-Only Memory (ROM) Design              | 85  |

|             | 5.3.1 Challenges of dynamic NAND ROM                    | 85  |

|             | 5.3.2 On-current to off-current plot                    | 87  |

|             | 5.3.3 A 32-stack dynamic NAND ROM with HVT bleeder      | 89  |

| 5.4         | Static NAND AND NAND-NOR ROM                            | 91  |

|             | 5.4.1 Investigating static ROM topologies               | 91  |

|             | 5.4.2 Static NAND ROM Monte Carlo Analysis              | 92  |

| 5.5         | Measurement Results                                     | 93  |

| 5.6         | Summary                                                 | 96  |

| VI. Pico-V  | Watt 2-Transistor Voltage Reference with Digital Trimma | -   |

| bility      |                                                         | 97  |

| 6.1         | Motivation and Previous Work                            | 97  |

| 6.2         | Contributions                                           | 100 |

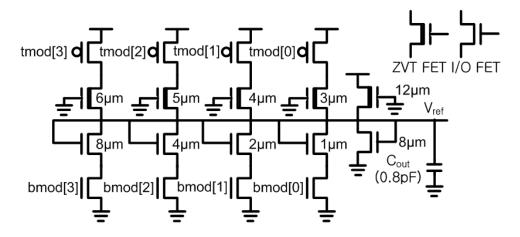

| 6.3         | Circuit Design                                          | 102 |

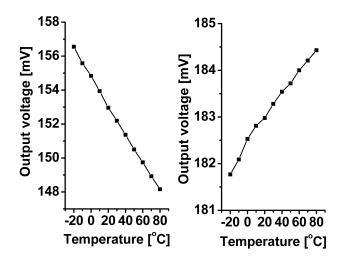

| 6.4         | 2T Reference Measured Results                           | 106 |

| 6.5         | Variability Analysis and Trimming Techniques            | 108 |

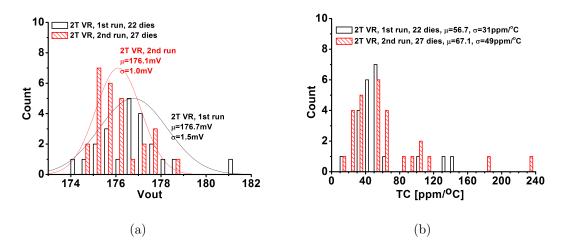

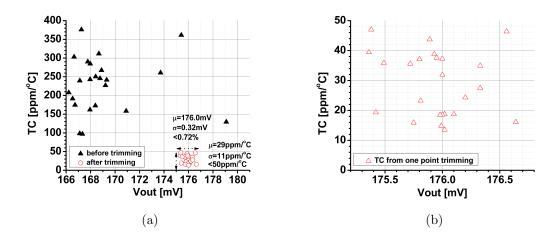

|             | 6.5.1 Statistical Measurement Results                   | 108 |

|             | 6.5.2 Digitally Trimmable 2T Voltage References         | 109 |

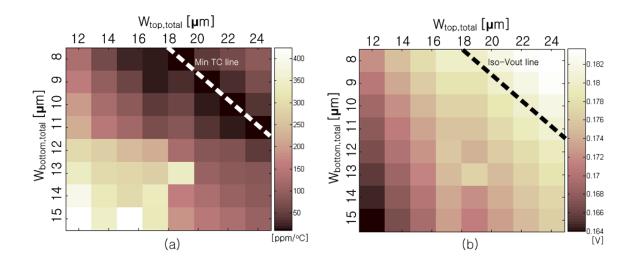

|             | 6.5.3 Analysis and Minimization of Trimming Cost        | 110 |

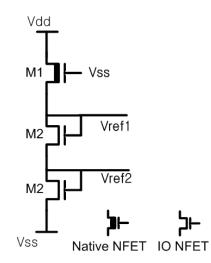

| 6.6         | Variant Designs of 2T Voltage References                | 113 |

| 6.7         | Technology Portability                                  | 116 |

| 6.8         | Summary                                                 | 117 |

| VII. 0.27V  | , 30MHz, 17.7nJ/transform, 1024-pt complex FFT Core     |     |

| with S      | Super-Pipelining                                        | 118 |

| 7.1         | Motivation and Previous Work                            | 118 |

| 7.2         | Contribution                                            | 118 |

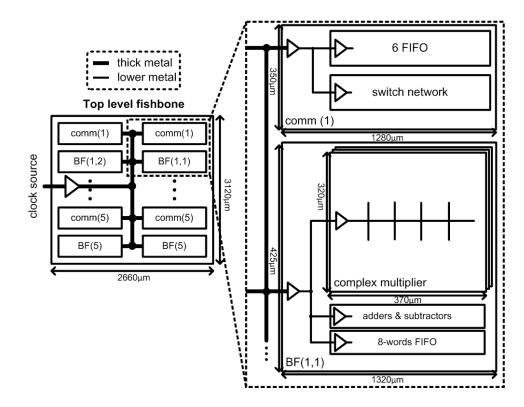

| 7.3         | Architecture Design                                     | 120 |

| 7.4         | Circuit designs                                         | 120 |

|             | 7.4.1 Super-Pipelining Technique and FIFO Design        | 120 |

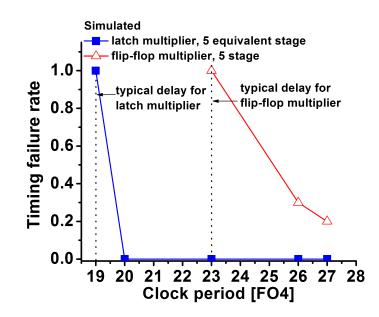

|             | 7.4.2 Two-Phase Latch for Less Delay Variability        | 123 |

|             | 7.4.3 Robust Clock Network Design                       | 125 |

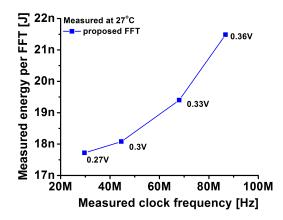

| 7.5         | Measurement Results and Comparisons                     | 127 |

| 7.6         | Summary                                                 | 128 |

| VIII. Robus | st Clock Network Design for Ultra Low Voltage Opera-    | 130 |

| 8.1       | Motivation and Previous Work                               | 130 |

|-----------|------------------------------------------------------------|-----|

| 8.2       | Contribution                                               | 131 |

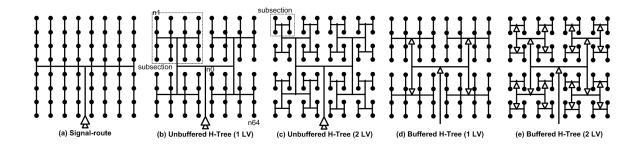

| 8.3       | Clock Network Comparison at Ultra Low Voltage Regimes      | 132 |

|           | 8.3.1 Comparison Frameworks                                | 132 |

|           | 8.3.2 Comparison at Nominal Conditions                     | 134 |

|           | 8.3.3 Impact of MOSFET Process Variations                  | 135 |

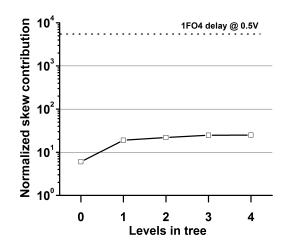

|           | 8.3.4 Impact of Interconnect Process Variations            | 137 |

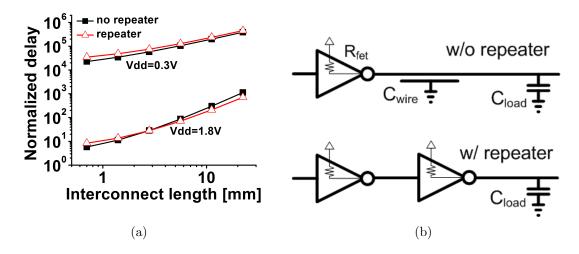

|           | 8.3.5 Driving Interconnects at Ultra Low Voltage Regimes   | 138 |

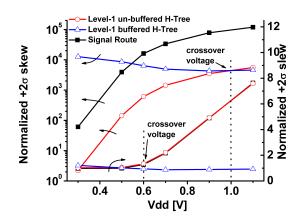

| 8.4       | Impact of Voltage and Technology Scaling                   | 139 |

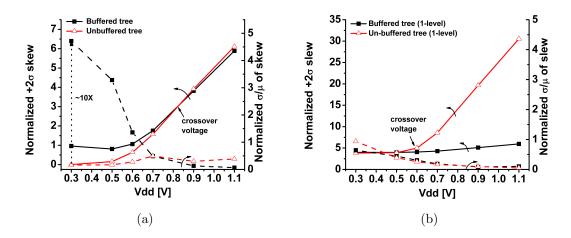

|           | 8.4.1 Supply Voltage Scaling                               | 140 |

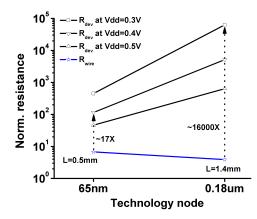

|           | 8.4.2 Technology Scaling                                   | 140 |

| 8.5       | Clock Network Design for a 16b MSP430-like Microcontroller | 142 |

| 8.6       | Summary                                                    | 145 |

| IX. Concl | usions                                                     | 146 |

| APPENDICE | $\mathbf{S}$                                               | 148 |

| BIBLIOGRA | РНҮ                                                        | 153 |

# LIST OF FIGURES

## Figure

| 1.1 | An implantable intra-ocular pressure sensor (courtesy of Y-S. Lin) .                                                                          | 2  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Supply voltage over technology scaling                                                                                                        | 5  |

| 1.3 | $V_{min}$ /Emin curve                                                                                                                         | 6  |

| 1.4 | Components that can directly benefit from the design methodologies of this work in cubic millimeter sensing systems (in gray) $\ldots \ldots$ | 12 |

| 1.5 | Energy efficiency improvement in the blocks of cubic millimeter sens-<br>ing systems                                                          | 12 |

| 2.1 | The Phoenix Processor                                                                                                                         | 17 |

| 2.2 | (a)Energy optimal technology matrix (b)Optimal $V_{DD}$ and energy over technologies                                                          | 21 |

| 2.3 | A typical power gating switch                                                                                                                 | 23 |

| 2.4 | Footer allocation in the Phoenix Processor                                                                                                    | 24 |

| 2.5 | CPU diagram                                                                                                                                   | 25 |

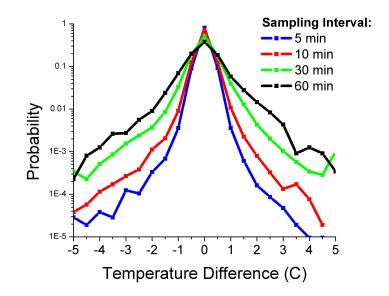

| 2.6 | Distribution of temperature in Muskegon, MI in 2006 represented as the difference between temporally adjacent measurements $[1]$              | 27 |

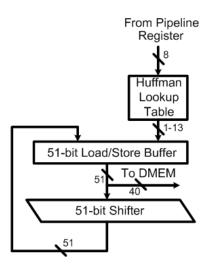

| 2.7 | Hardware support for compression.                                                                                                             | 28 |

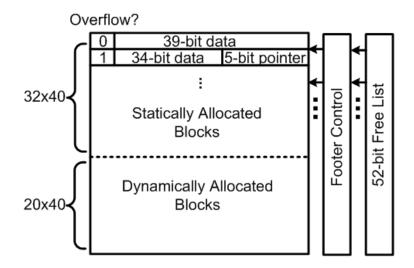

| 2.8 | Memory support for compression                                                                                                                | 29 |

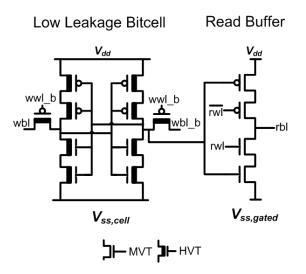

| 2.9 | Proposed ultra low standby power SRAM cell                                                                                                    | 31 |

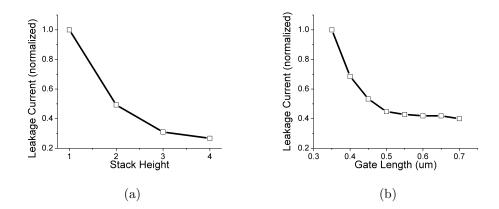

| 2.10 | Effectiveness of (a) stack forcing and (b) gate length biasing for leak-<br>age reduction                                                               | 31 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----|

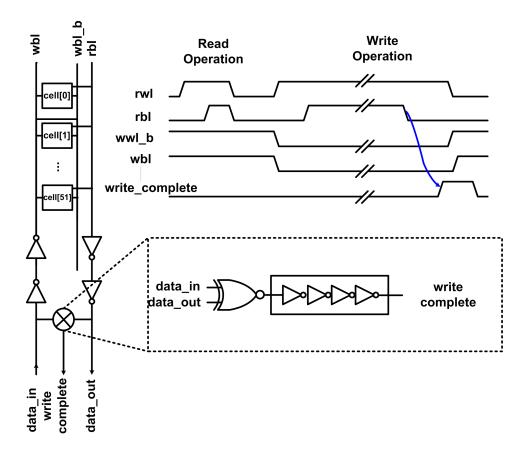

| 2.11 | Memory column diagram showing completion detection                                                                                                      | 32 |

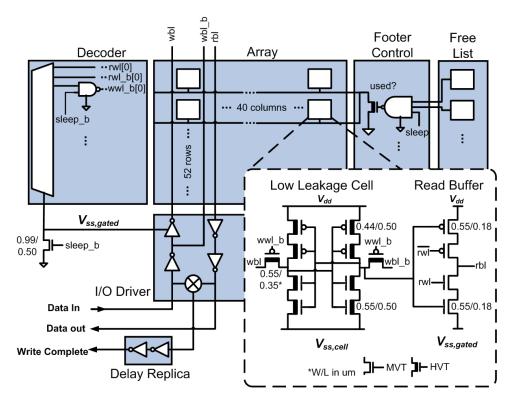

| 2.12 | SRAM array architecture for Data SRAM (DMEM)                                                                                                            | 33 |

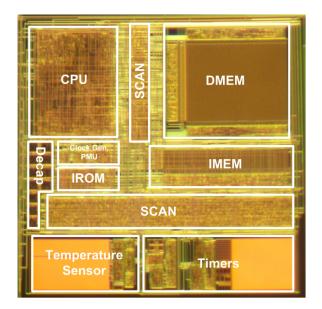

| 2.13 | Phoenix Processor die photo                                                                                                                             | 34 |

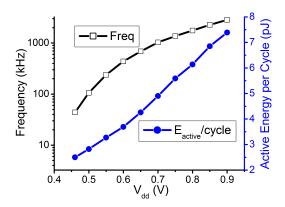

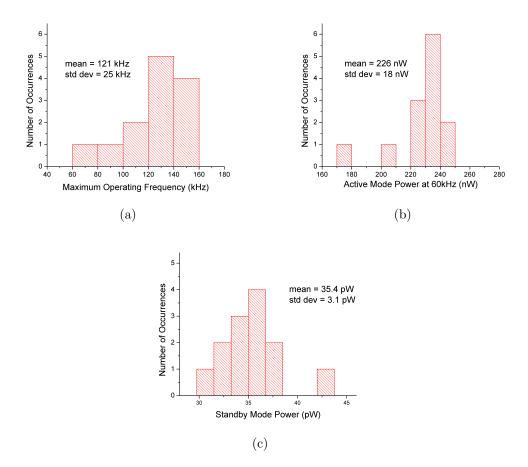

| 2.14 | Measured frequency and energy consumption                                                                                                               | 35 |

| 2.15 | Measured (a) frequency distribution (b) active mode power distribu-<br>tion at 60 kHz (c) standby mode power distribution for 13 dies at $V_{DD}=0.5$ V | 36 |

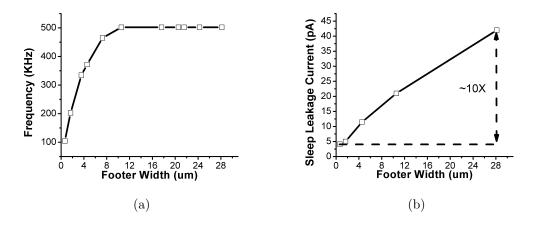

| 2.16 | Measured (a) frequency and (b) standby leakage as functions of Cen-<br>tral Processing Unit (CPU) footer width                                          | 38 |

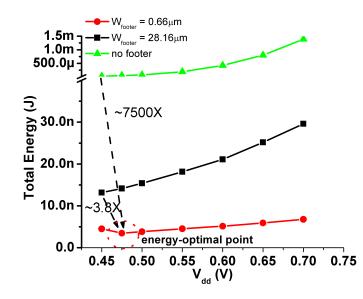

| 2.17 | Total energy consumption assuming 1000 instructions are executed every 10 minutes                                                                       | 38 |

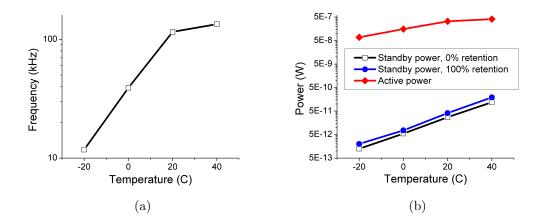

| 2.18 | Measured (a) frequency and (b) power as functions of temperature.                                                                                       | 40 |

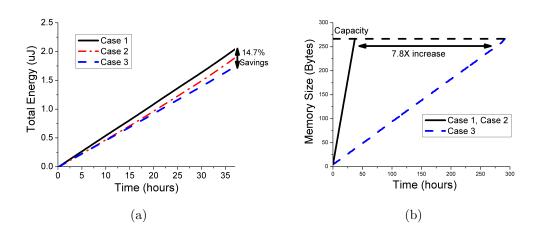

| 2.19 | Computed time profiles of (a) energy and (b) memory size for a temperature measurement routine                                                          | 40 |

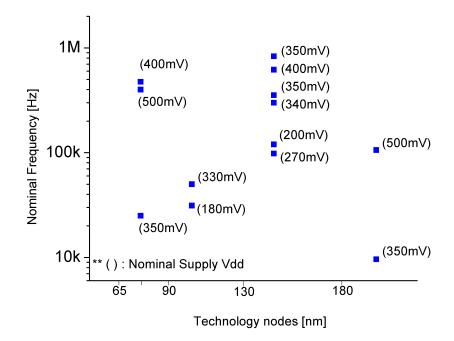

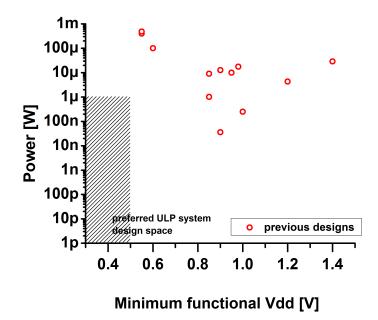

| 3.1  | Published sub- or near-threshold VLSI designs                                                                                                           | 43 |

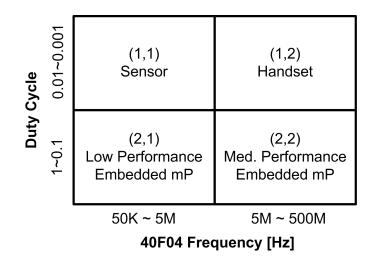

| 3.2  | Application spaces in ultra low voltage operation.                                                                                                      | 45 |

| 3.3  | Basic technology selection for (a) logic (b) SRAM                                                                                                       | 48 |

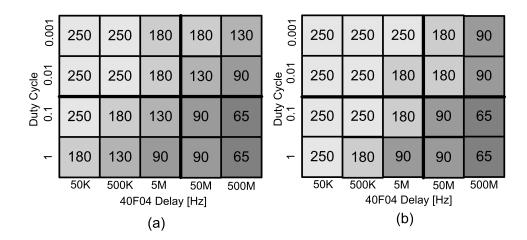

| 3.4  | $E_{min}$ and standby leakage current over leakage reduction ratio ( $E_{min}$ shows small dip due to virtual ground bounce)                            | 49 |

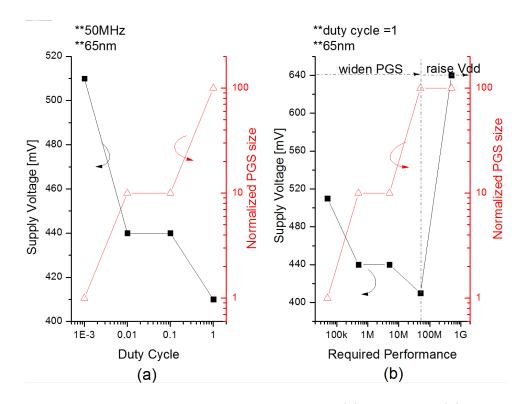

| 3.5  | Result of co-optimization with sweeping (a) duty cycle (b) required performance                                                                         | 50 |

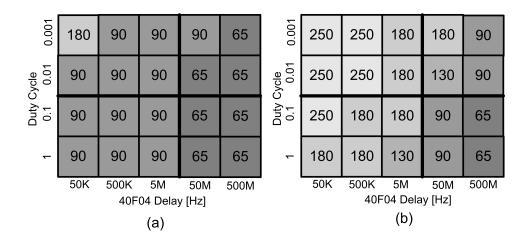

| 3.6  | Optimal technology selection (a) for logic with co-optimized $V_{DD}$ /PGS, (b) for SRAM with 10x leakage reduction                                     | 51 |

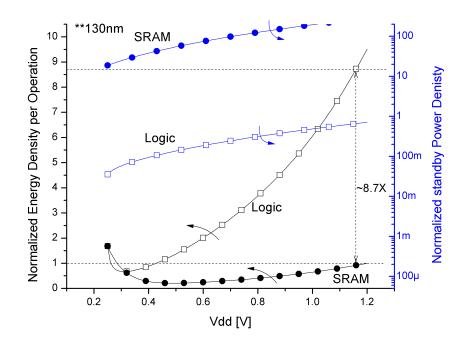

| 3.7  | Energy density per operation and standby power density $\ldots$ .                                                                                       | 52 |

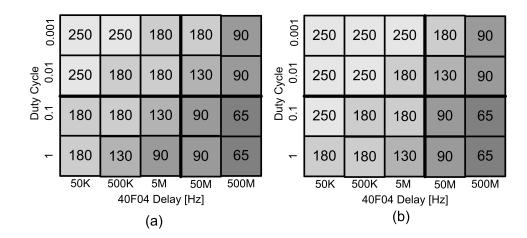

| 3.8  | Energy optimal technology selection with SRAM/logic area ratios of (a) 0.5 (b) 0.8                                                                      | 53 |

| 3.9  | (a) Worst energy technology selection for SRAM ratio of 0.8 (b) energy saving ratio $[\times]$ by moving to Figure 3.8(b)                                                                                | 53        |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

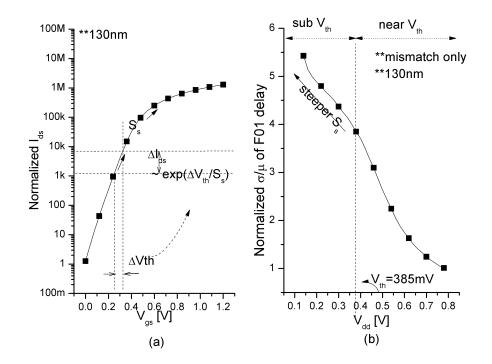

| 3.10 | (a) Log $I_{ds}$ - $V_{gs}$ curve, (b) change of variation depending on operating point                                                                                                                  | 55        |

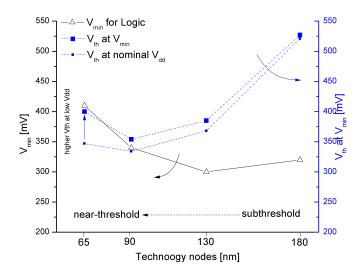

| 3.11 | Optimal energy operation point over technologies                                                                                                                                                         | 56        |

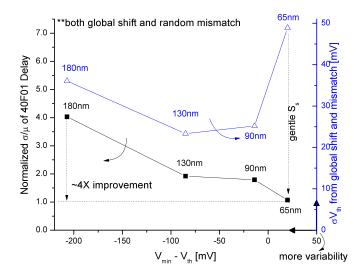

| 3.12 | variability as a function of technology choice $\ldots \ldots \ldots \ldots \ldots$                                                                                                                      | 57        |

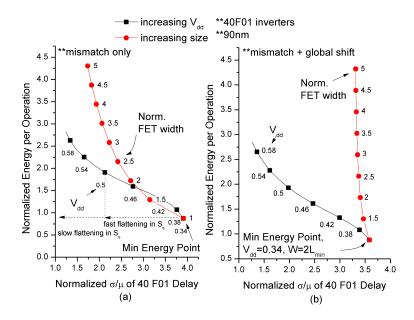

| 3.13 | (a) Mismatch-only (b) die-to-die and mismatch, energy per operation increase with less variability                                                                                                       | 58        |

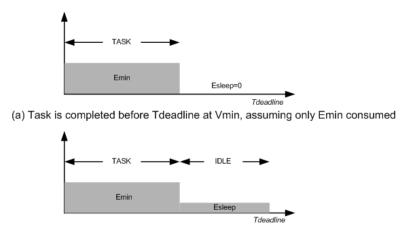

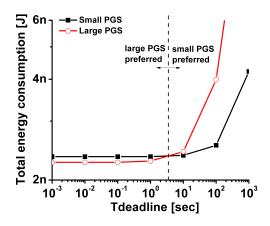

| 4.1  | Illustration of task scheduling at different deadlines $\ldots \ldots \ldots$                                                                                                                            | 61        |

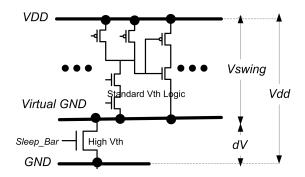

| 4.2  | Basic PGS configuration                                                                                                                                                                                  | 63        |

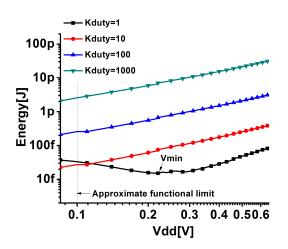

| 4.3  | $V_{min}/E_{min}$ curves with different $K_{duty}$ considering sleep energy                                                                                                                              | 63        |

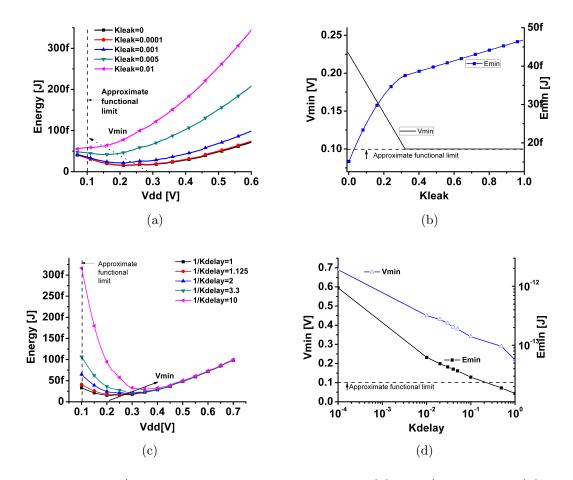

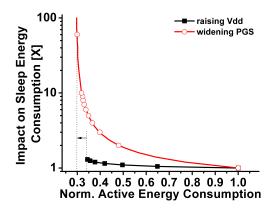

| 4.4  | $V_{min} / E_{min}$ change with $K_{leak}$ and $K_{delay}$ , (a) $V_{min} / E_{min}$ curves (b) $K_{leak}$ - $V_{min} / E_{min}$ , (c) $V_{min} / E_{min}$ curves, (d) $K_{delay}$ - $V_{min} / E_{min}$ | 66        |

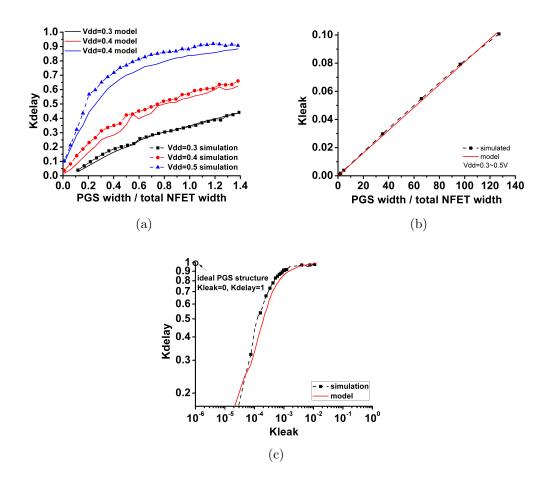

| 4.5  | $K_{leak}$ and $K_{delay}$ change with PGS width and $V_{DD}$ , (a) width - $K_{delay}$ (b)width - $K_{leak}$ (c) $K_{leak}$ $K_{delay}$                                                                 | 68        |

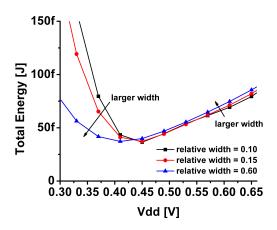

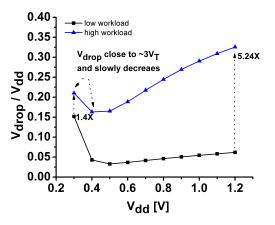

| 4.6  | $V_{min} / E_{min}$ with different PGS sizes, $K_{duty} = 100 \dots \dots \dots \dots$                                                                                                                   | 70        |

| 4.7  | Comparison between raising $V_{DD}$ and upsizing PGS in energy optimization                                                                                                                              | 71        |

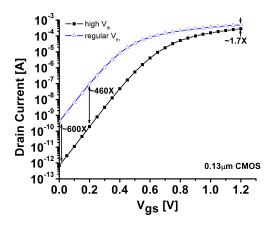

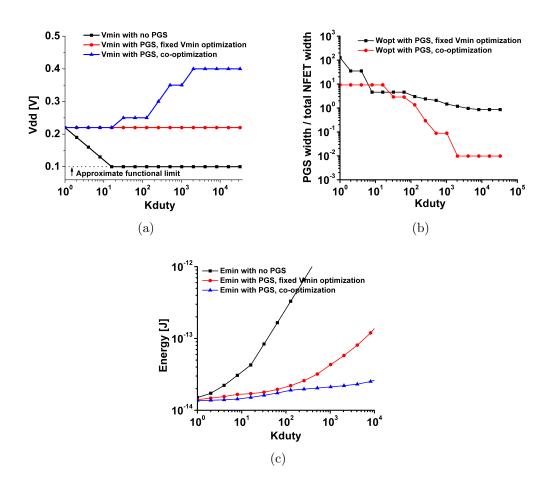

| 4.8  | On/off-current of high $V_{th}$ and regular $V_{th}$ devices $\ldots$ $\ldots$ $\ldots$                                                                                                                  | 72        |

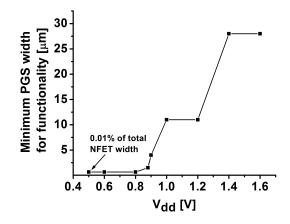

| 4.9  | Off-current vs. on-current as sweeping PGS width                                                                                                                                                         | 72        |

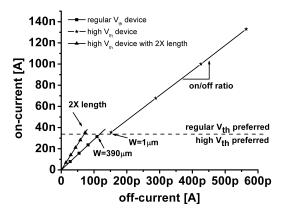

| 4.10 | New $V_{min}$ and optimal PGS size at different $K_{duty}$                                                                                                                                               | 74        |

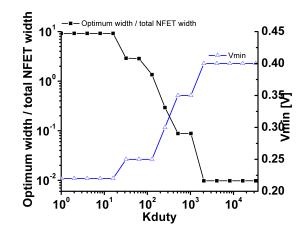

| 4.11 | Comparison of three optimization strategies, (a) $K_{duty}V_{min}$ (b) $K_{duty}$ optim<br>PGS width (c) $K_{duty}E_{min}$                                                                               | mal<br>76 |

| 4.12 | Measured total energy consumption with two different PGS sizes from a test microprocessor                                                                                                                | 77        |

| 4.13 | Measured minimal PGS size for functionality                                                                                                                                                              | 79        |

| 4.14 | Simulated virtual ground level over different workload and supply voltage                                                                           | 80  |

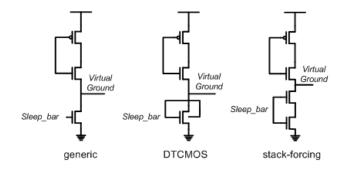

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.15 | Generic, DTCMOS, and stack-forcing PGS                                                                                                              | 81  |

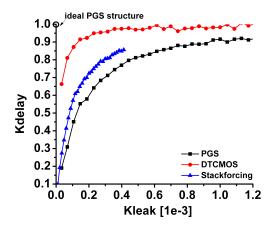

| 4.16 | $K_{leak}$ - $K_{delay}$ curves with different PGSs                                                                                                 | 81  |

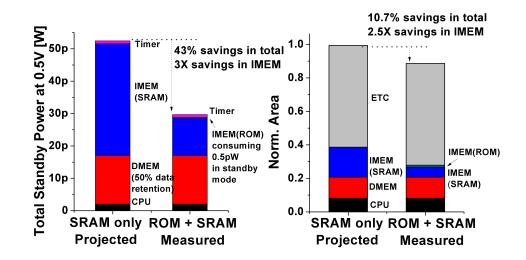

| 5.1  | Power(left) and area(right) comparisons for SRAM-only Instruction SRAM (IMEM) (projected) and an SRAM/ROM hybrid IMEM (measured).                   | 84  |

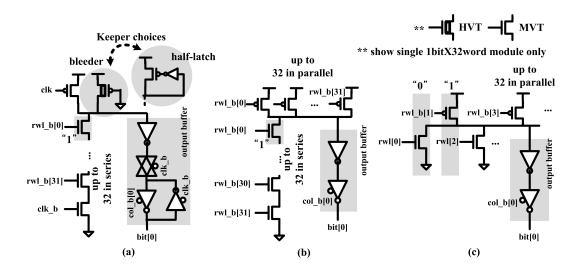

| 5.2  | Schematics of three ROMs for ultra low voltage: (a) dynamic NAND, (b) static NAND, (c) static NAND-NOR                                              | 85  |

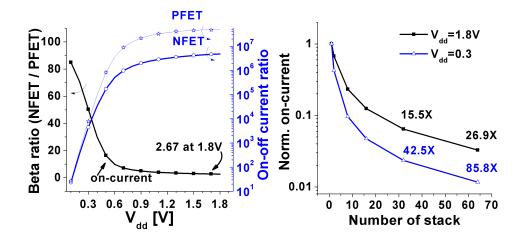

| 5.3  | Beta ratio and on- to off-current ratio (left), on-current reduction over number of stack (for minimum-sized FET) (right) $\ldots \ldots$           | 86  |

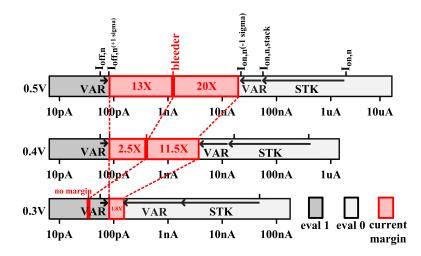

| 5.4  | Current margin plot for 32-stack dynamic NAND ROM with HVT bleeder                                                                                  | 88  |

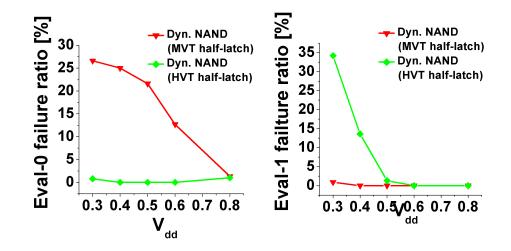

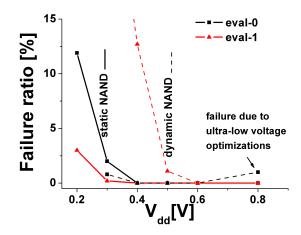

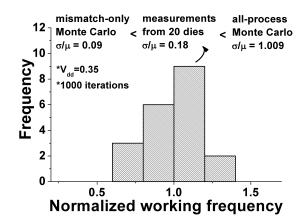

| 5.5  | Failure rate for the dynamic NAND with half-latches. (1000 Monte Carlo iterations with die-to-die and mismatch variations)                          | 90  |

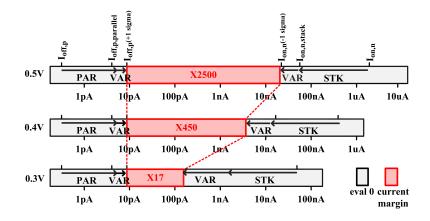

| 5.6  | Current margin plot for 32-stack static NAND ROM                                                                                                    | 92  |

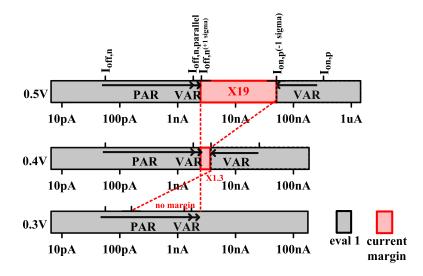

| 5.7  | Current margin plot for 32-leg static NAND-NOR ROM $\ . \ . \ . \ .$                                                                                | 93  |

| 5.8  | 1000 Monte Carlo Simulation Program with Integrated Circuit Emphasis (SPICE) simulations for two ROM topologies considering mismatch and die-to-die | 94  |

| 5.9  | Histogram of operating frequency of static NAND ROM                                                                                                 | 94  |

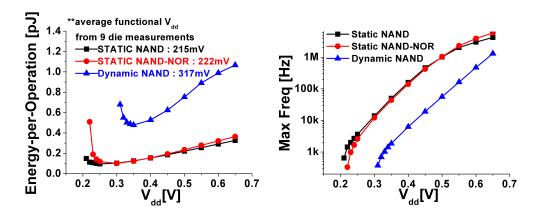

| 5.10 | Measured energy-per-operation and frequency                                                                                                         | 95  |

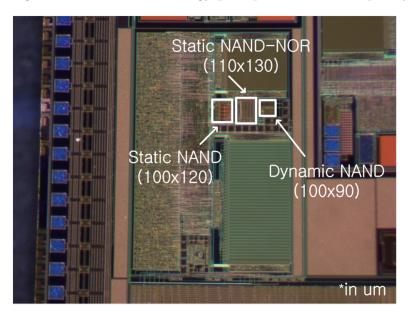

| 5.11 | Die photo and dimensions                                                                                                                            | 95  |

| 6.1  | Power and minimal functional supply voltage comparisons $\ldots$ .                                                                                  | 99  |

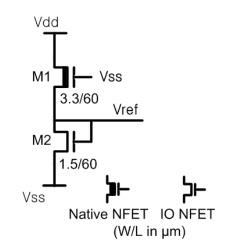

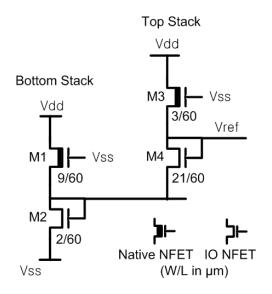

| 6.2  | Schematics of a 2T voltage reference                                                                                                                | 101 |

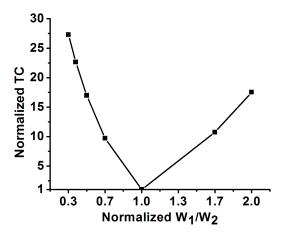

| 6.3  | Proper sizing of two transistors minimizes temperature dependency (simulated results).                                                              | 103 |

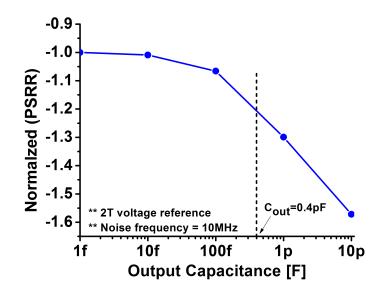

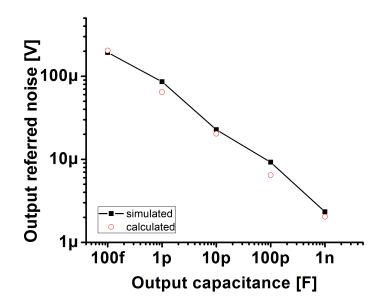

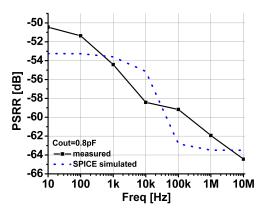

| 6.4  | A larger output capacitor provides better PSRR (simulated results)                                                                                  | 104 |

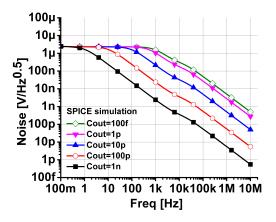

| 6.5  | Simulated output referred noise of a 2T voltage reference with differ-<br>ent output capacitors                                                        | 105   |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

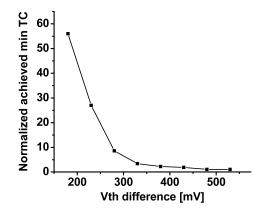

| 6.6  | Simulated required $V_{th}$ difference for proper operations $\ldots \ldots \ldots$                                                                    | 106   |

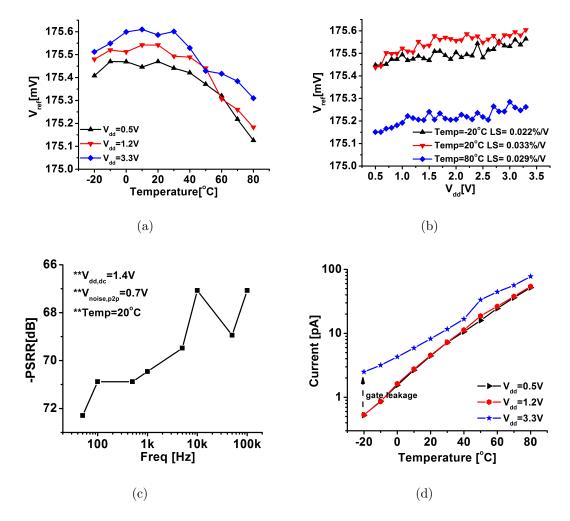

| 6.7  | Measured (a) temperature coefficient (b) line sensitivity (c) power<br>supply rejection ratio (d) current consumption of the 2T voltage ref-<br>erence | 107   |

| 6.8  | Measured (a) output voltage (b) temperature coefficient distribution of the 2T voltage references in two separate runs                                 | 109   |

| 6.9  | Figure 13 Schematics of trimmable 2T voltage reference                                                                                                 | 111   |

| 6.10 | Measured (a) TC and (b) output voltage change with trim settings                                                                                       | 111   |

| 6.11 | (a) Measured reductions of output voltage and temperature coefficient spreads (b) zoomed view                                                          | 112   |

| 6.12 | Measured PSRR of the trimmable 2T voltage reference $\ldots$                                                                                           | 113   |

| 6.13 | Simulated output referred noise of the trimmable 2T voltage reference                                                                                  | e 113 |

| 6.14 | Schematics of 4T voltage reference                                                                                                                     | 114   |

| 6.15 | schematics of 2T voltage reference for lower output voltage $\ . \ . \ .$                                                                              | 115   |

| 6.16 | Measured temperature coefficients achieved by skewing the size of transistors                                                                          | 115   |

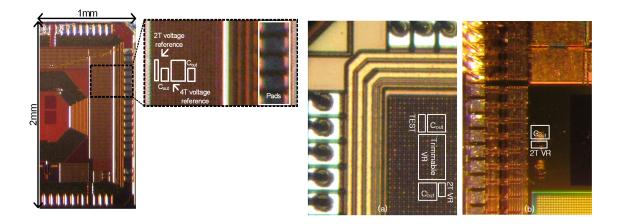

| 6.17 | Die micrographs; (a) 1st $0.13\mu m$ run, (b) 2nd $0.13\mu m$ run, (c) $0.18\mu m$ run, (d) 65nm run                                                   | 117   |

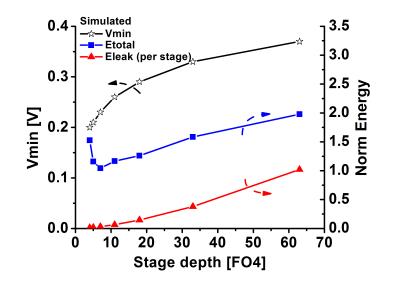

| 7.1  | Effect of pipeline depth on energy consumption                                                                                                         | 119   |

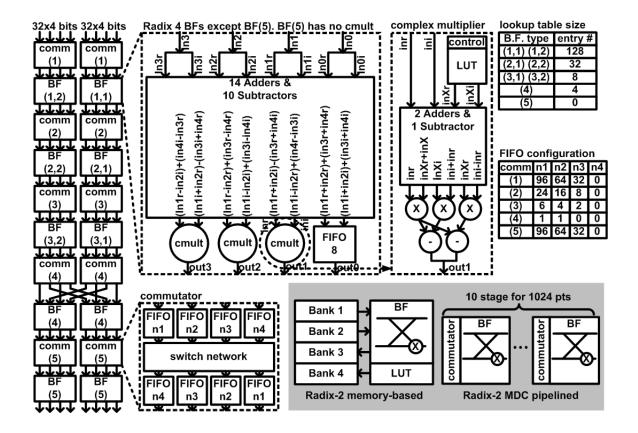

| 7.2  | A pipelined, 8×32b input, radix-4, 2-lane, 1024-pt, complex FFT architecture                                                                           | 121   |

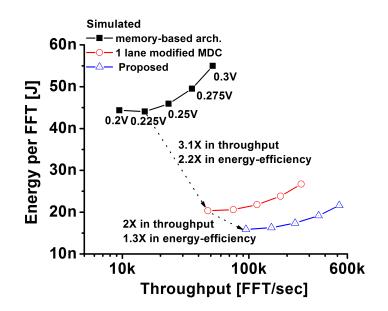

| 7.3  | Energy and throughput improvement by architecture modifictions .                                                                                       | 121   |

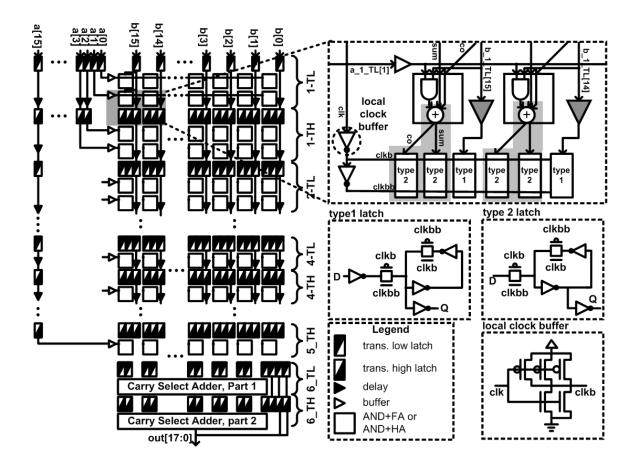

| 7.4  | A 16b Baugh-Wooley multiplier is super-pipelined with 2-phase latches                                                                                  | s122  |

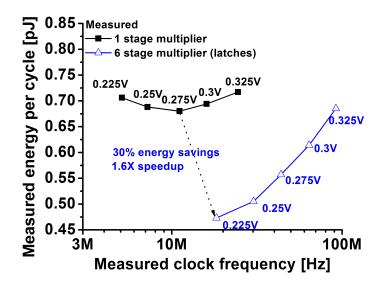

| 7.5  | Measured energy consumption of differently pipelined multipliers                                                                                       | 123   |

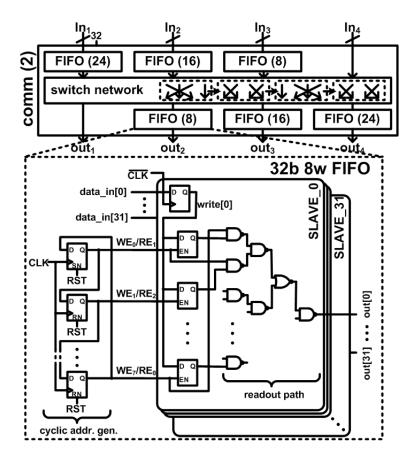

| 7.6  | Schematics of commutators and FIFOs                                                                              | 124  |

|------|------------------------------------------------------------------------------------------------------------------|------|

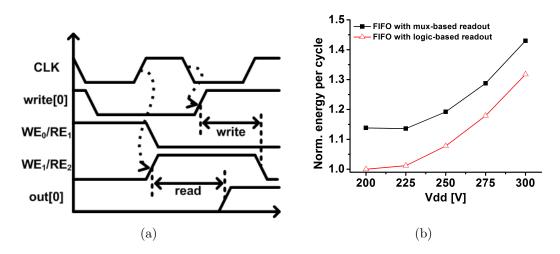

| 7.7  | (a) Waveform of operation (b) FIFO energy consumption comparison.                                                | 124  |

| 7.8  | Timing failure rates across Monte-Carlo simulations with random process variations fro two pipelined multipliers | 125  |

| 7.9  | Proposed clock network design with limited buffers and matched in-<br>terconnects                                | 126  |

| 7.10 | Measured energy consumption and performance of the proposed FFT core                                             | 127  |

| 7.11 | Die photo of the FFT core implemented in 65nm CMOS $\ldots$ .                                                    | 129  |

| 8.1  | Clock network topologies                                                                                         | 132  |

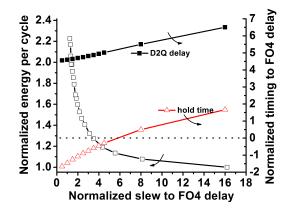

| 8.2  | Tradeoff between slew and clock network energy $\hdots$                                                          | 133  |

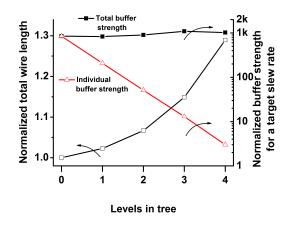

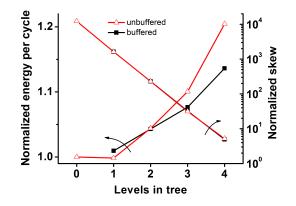

| 8.3  | Wire length and required buffer                                                                                  | 134  |

| 8.4  | Energy and skew comparison of clock networks                                                                     | 135  |

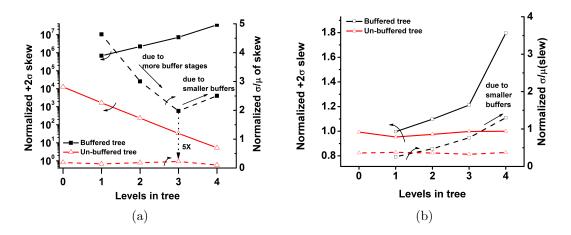

| 8.5  | (a) Skew with MOSFET variations, (b) Slew with MOSFET variations.                                                | .136 |

| 8.6  | Skew contribution from interconnect variations                                                                   | 138  |

| 8.7  | Driving a long interconnect without repeaters (a) delay comparison,<br>(b) schematics.                           | 139  |

| 8.8  | Impact of voltage scaling on (a) skew, (b) slew.                                                                 | 140  |

| 8.9  | Resistance scaling across technologies                                                                           | 141  |

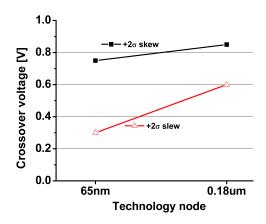

| 8.10 | Crossover voltages for $+2\sigma$ skew and slew                                                                  | 142  |

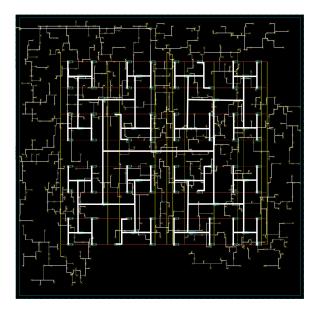

| 8.11 | Layout view for the APR-ed microprocessor with 3-level buffered H-<br>Tree clock network                         | 143  |

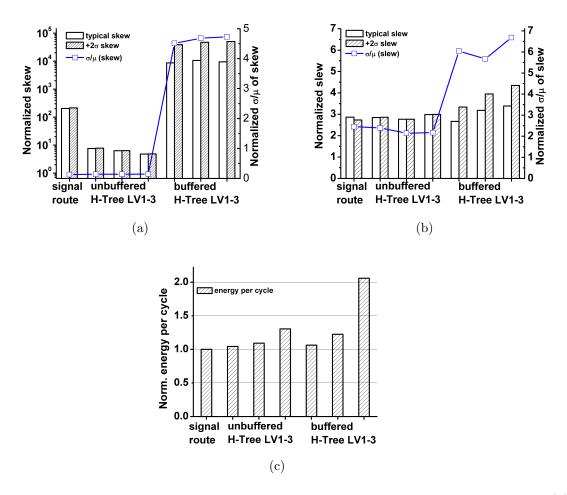

| 8.12 | Comparison for the clock networks of the 16b microcontroller on (a) skew, (b) slew, (c) energy consumption       | 144  |

| 8.13 | Optimal clock network across supply voltages                                                                     | 145  |

# LIST OF TABLES

## <u>Table</u>

| 2.1 | Instruction set architecture overview.                              | 26  |

|-----|---------------------------------------------------------------------|-----|

| 2.2 | Comparison to other low voltage microcontroller                     | 36  |

| 6.1 | Recent published designs of low power voltage references $\ldots$ . | 99  |

| 6.2 | Measurement summary of the proposed 2T voltage references           | 116 |

| 7.1 | RC mismatch in clock network                                        | 126 |

| 7.2 | Comparison of the proposed FFT core                                 | 127 |

| 7.3 | Measurement summary of the proposed FFT core                        | 128 |

## LIST OF ABBREVIATIONS

A/D Analog to Digital

CMOS Complementary Metal-Oxide-Semiconductor

**CPU** Central Processing Unit

**DMEM** Data SRAM

**DSP** Digital Signal Processing

${\bf FFT}$  Fast Fourier Transform

FO4 Fan-Out-of-4

**ISA** Instruction Set Architecture

${\bf IROM}$  Instruction ROM

**IMEM** Instruction SRAM

**IC** Integrated Circuit

**I/O** Input and Output

LS Line Sensitivity

MDC Multi-Path Delay Commutator

**MEMS** Micro Electro Mechanical Systems

**MOSFET** Metal-Oxide-Semiconductor Field Effect Transistor

**NFET** Negative Channel Field Effect Transistor

**PFET** Positive Channel Field Effect Transistor

**PGS** Power Gating Switch

**PSRR** Power Supply Rejection Ratio

**PMU** Power Management Unit

**PVT** Process, Voltage and Temperature

**ROM** Read-Only Memory

${\bf RF}\,$  Radio Frequency

**SRAM** Static Random-Access Memory

**SPICE** Simulation Program with Integrated Circuit Emphasis

${\bf VLSI}\,$  Very Large Scale Integration

$V_{th}$  Threshold Voltage

$V_t$  Thermal Voltage

## ABSTRACT

Extreme Power-Constrained Integrated Circuit Design

by

Mingoo Seok

Chair: Dennis Michael Sylvester

Recently sensing systems of cubic millimeter scale have gained significant attention since they may be embedded virtually anywhere. Particularly, biomedical devices for implanting in human bodies to monitor critical vital signals, are one of the most promising applications of such small scale systems. For developing these systems, there are two challenging requirements; 1) long lifetime for minimal maintenance (e.g., additional surgeries) and 2) small volume for less invasive deployments. Ultra low power circuits are key enablers for these requirements since they ensure longer lifetime and minimize the volume of power sources, which often occupy the dominant portion of system volume.

Voltage scaling is one promising measure for reducing energy consumption of integrated circuits. Scaling supply voltage down to near, or below, the transistor threshold voltage has been shown to provide  $10-20 \times$  energy savings compared to nominal voltage operations. However, supply voltage scaling is not a complete solution to developing a cubic millimeter sensing system since it brings up many challenges, including minimizing standby power, designing key analog building blocks with constrained power budgets, and improving delay variability, performance, and energy efficiency beyond simple voltage scaling.

This thesis presents new circuit and architecture design approaches to overcome voltage scaling challenges and realize cubic millimeter sensing systems. Our proposed approaches yield record-setting energy efficiencies with numerous silicon demonstration vehicles to prove their efficacy.

We first describe the Phoenix Processor, a sensing platform for demonstrating standby power minimization techniques such as minimally-sized power gating switches and ultra-low leakage memory arrays. A test chip that includes an 8b microcontroller, embedded memories, a timer and temperature sensor, demonstrates a standby power of 35pW, which is 2-3 orders of magnitude lower than previously reported sensor processors.

As a key analog building block for use in many sensing systems, we also propose an ultra low power voltage reference. Test chips, extensively verified in 3 different semiconductor technologies across four different fabrication runs, typically consume down to 2.2pW, or  $16000 \times$  smaller than previous designs, without compromising temperature, supply voltage, and process stability.

Finally, a Fast-Fourier-Transform (FFT) core is designed to demonstrate techniques for improving performance, variability tolerance, and energy efficiency beyond conventional voltage scaling. A test chips in 65nm CMOS consumes a record-low 17.7nJ/FFT, at least  $4 \times$  lower than prior state-of-the-art, and operates at 30MHz at only 0.27V.

## CHAPTER I

## Introduction

## **1.1 Emerging Sensing Applications**

Continued advances in electronics design enable wireless sensing systems, which source environmental data (e.g., temperature) and wirelessly transmit for further processing and data aggregation. Such designs, which can have volumes on the order of several cubic centimeters, have been proposed by both academics and industry. For example, a sensing system [28] can be used to monitor soil moisture for crop irrigation. Also, the pressure inside car tires can be measured by a sensor [32] to notify drivers of any problems. Another example is a pressure sensor [18] designed for monitoring the integrity of stent grafts in arteries. Along with companies, several universities have demonstrated sensing systems including wireless sensors for neural monitoring and stimulation, as well as [108, 38] Micro Electro Mechanical Systems (MEMS) sensors for gas detection [112].

With the success of cubic centimeter sensing systems, there is an emerging demand for smaller sensing systems at the cubic millimeter scale that can be embedded virtually anywhere due to its small volume. We envision a system that includes microprocessors, sensors, actuators, power sources, and radio within the volume constraint of several cubic millimeters. This size microsystem can be easily implanted inside human bodies, construction materials, and clothing, enabling a new set of applications.

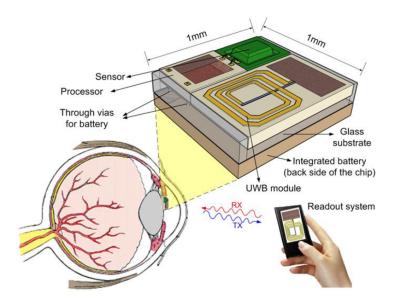

Figure 1.1: An implantable intra-ocular pressure sensor (courtesy of Y-S. Lin)

Aligned with this interest, at the University of Michigan there have been multiyear research projects to develop biomedical sensor systems for the diagnosis and treatment of Glaucoma [63], as illustrated in Figure 1.1. The diagnosis and treatment of Glaucoma disease is expected to help 60.5 million people worldwide by 2010 [34]. However, currently doctors must perform periodic measurements of pressure in the eye (intra-ocular pressure), requiring patents to make frequent trips to a doctor's office to ensure sufficient temporal resolution of measurements [82]. A cubic millimeter scale sensing system that can be implanted inside a human eye can reduce cost while providing better patient care. In addition to Glaucoma, cubic millimeter sensing systems can potentially benefit a wide range of biomedical applications such as the monitoring of heart and brain signals.

While less volume constrained than biomedical applications, a wide range of general wireless sensing systems could leverage cubic millimeter sensing systems, including surveillance systems used in battlefield monitoring [104, 2]. In addition, small scale sensing systems can be mixed into construction materials (e.g., cement) without impacting their integrity in order to monitor the heat transfer within buildings in a fine-grained fashion.

# 1.2 Challenges of Achieving Cubic Millimeter Scale Sensing Systems

To achieve such a small scale sensing system, it is critical to miniaturize all building blocks such as microprocessors, memories, radios, sensors, actuators, and power sources. Continuous reduction of minimum feature size of silicon technology, dictated by Moore's Law, enables building circuit components (e.g., microprocessors, memories, radios) on a cubic millimeter scale. Similarly, advances in MEMS technology have enabled small scale sensors and actuators for meeting the volume constraints of cubic millimeter sensing systems.

However, power source improvements, in both batteries and energy scavengers [55], are much less dramatic. Although recent advances in compact batteries [7] allow for a cubic millimeter power source, the amount of energy stored by the micro battery is also reduced roughly proportionally to the battery volume, imposing a challenge on overall power consumption of the sensing system.

Along with the miniaturization of each component, ensuring long lifetime is equally critical. Since the sensing systems are likely to be embedded in poorly accessible locations (e.g., inside human body or inside building walls), short lifetime lead to higher maintenance costs, reducing the feasibility of such systems.

To meet the volume and lifetime constraints of cubic millimeter sensing systems, ultra low power design of circuits and MEMS components is a key enabler. Ultra low power consumption may allow the use of millimeter scale power sources while enabling lifetime of several years. We can estimate the power budget of a sensing system for guaranteeing one year of lifetime when it is powered by a cubic millimeter power source. Based on a thin film zinc/silver oxide battery with capacity of  $100\mu Ah/mm^2$  and output voltage of 1.55V [63], the entire sensing system should consume less than 177pW on average for a one year lifetime. This extremely small power consumption is several orders of magnitude lower than what most energy efficient commercial microprocessors, such as Texas Instruments MSP430, consume in their standby modes [94].

Given this power-limited design space, this thesis focuses on circuit and architectural techniques for extremely power constrained Integrated Circuit (IC) design. In the remainder of this chapter, ultra low voltage operation to minimize power consumption is reviewed. Then, the challenges to operating ICs in the ultra low voltage regime are identified and the contributions of this work are discussed.

## **1.3** Reducing Power Consumption in ICs

#### 1.3.1 Power Consumption in Modern IC design

Power consumption has been a critical issue in integrated circuit design as it sharply increases in modern sub-micron device technologies. Ideal technology scaling reduces energy in the third order as shown in EQ 1.1. However, achieving such energy gains is not practical for two reasons. First, switching energy is no longer the dominant factor of total energy consumption due to the rapid increase of subthreshold and gate leakage components in modern Metal-Oxide-Semiconductor Field Effect Transistor (MOSFET)s. Second, much slower supply voltage scaling in recent technologies provides only a linear reduction in switching energy.

$$Delay = \frac{1}{f} = \frac{C_s V_{DD}}{I_{dsat}} \propto \frac{V_{DD}}{(V_{DD} - V_{th})^{1.3}} \quad Power \propto f V_{DD}^2 \quad Energy \propto C_s \cdot V_{DD}^2 \quad (1.1)$$

Supply voltage scaling requires Threshold Voltage  $(V_{th})$  scaling to maintain the similar gate overdrive  $(V_{DD} - V_{th})$  of MOSFETs, which dictates transistor perfor-

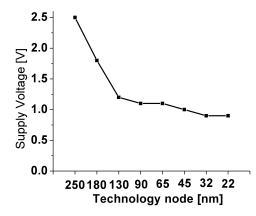

Figure 1.2: Supply voltage over technology scaling

mance. However, as shown in Figure 1.2, supply voltage has held nearly constant around 1V for the last several technology nodes since  $V_{th}$  scaling in those nodes leads to prohibitively large subthreshold leakage current. The stagnation of supply voltage scaling and increasing leakage energy result in worsening energy efficiency with technology scaling.

#### 1.3.2 Ultra Low Voltage Operation

Voltage scaling technique has been a promising method to minimize energy consumed in circuits. As the supply voltage scales, quadratic to exponential energy savings in switching, subthreshold leakage, and gate leakage energy can be achieved. However, as pointed out in EQ 1.1, the scaled supply voltage directly degrades circuit performance. Therefore, dynamic voltage scaling is sometimes employed where supply voltage is lowered to a point where circuits can finish a task just before a known deadline. The lower limit of supply voltage with performance constraints usually falls well above the  $V_{th}$  of MOSFETs, as shown in [96, 109, 76].

However, we can scale the supply voltage further down to near or below the  $V_{th}$  (thereafter this is referred to as the ultra low voltage regime) to maximize energy efficiency since CMOS gates are known to be functional in this regime [66]. Recently

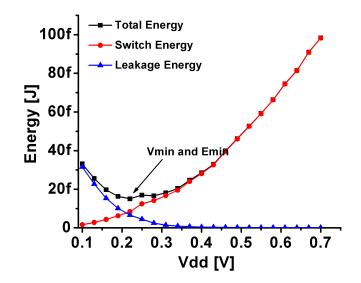

Figure 1.3:  $V_{min}$ /Emin curve

several researchers successfully demonstrate CMOS ICs operating at several hundreds of millivolts with several orders of magnitude better energy efficiency [102, 36, 41, 57].

One of the foundational concepts in ultra low voltage circuit design centers around a peak energy-efficient operating point. Zhai et al., [113] and Calhoun et al., [15] showed that energy-efficiency degrades when supply voltage is scaled too low since an increasingly slow circuit consumes substantial leakage energy, offsetting the quadratic savings in switching energy. Therefore, the total energy consumption begins to increase once the supply voltage scales down below a certain point, which we refer to as  $V_{min}$ . The optimal energy consumption, which occurs at  $V_{min}$ , is defined as  $E_{min}$ . This relationship is illustrated in Figure 1.3. The  $V_{min}$  often lies at 300-400mV for circuits in modern sub-micron CMOS technologies.

From these early studies on the energy optimal point, various aspects of design including technology, circuit, and architecture techniques have been actively researched for achieving better energy efficiency, robustness, and performance. At the technology level, several approaches for device design have been proposed [74, 35] since modern processes are sub-optimal for ultra low voltage operation as they are optimized for high performance applications. Circuit-level studies include how to size MOSFETs for minimizing energy [17], reducing variability [56], and enhancing performance [48]. Additionally, Static Random-Access Memory (SRAM) has been intensively studied since its positive feedback structure suffers from degraded stability at the reduced on-current to off-current ratio found in the ultra low voltage regime. In particular, different topologies including a single-ended 6T [114], 8T [100], and 10T [16, 21] SRAM have been proposed to replace the conventional differential 6T structure. By employing design techniques for ultra low voltage operation, several computational cores [102, 41] and general microprocessors have been published that achieve performance of hundreds of kHz and energy consumption of several pJ per cycle [36, 57].

## **1.4** Challenges and Contributions

#### 1.4.1 Minimizing Standby Power

It is exciting that a microprocessor consumes only several pico-joules per cycle or hundreds of nanowatt at ultra low voltage regimes, compared to 85pJ per cycle or tens of microwatt consumed by a state-of-art low power microprocessor [27]. Although the performance of hundreds of kHz is much slower, it is adequate for cubic millimeter sensing systems. However, simple voltage scaling is not sufficient to reduce the power consumption down to the level of hundreds of pico-watt that cubic millimeter sensing systems require as discussed in Section 1.2.

To meet the stringent power constraints, we find that it is critical to reduce standby power since cubic millimeter sensing systems spend most of their lifetime in waiting for periodic workloads to perform and hence the total energy consumption is dominated by standby mode. Our investigation with a 0.35V energy efficient microcontroller [36] indicates that it is necessary to reduce the standby power by 2-3 orders of magnitude for achieving an average power of several hundreds of picowatt. However, standby power has been largely overlooked in ultra low voltage design space despite of its importance. Therefore, we first focus on minimizing standby power consumption along with high energy efficiency in active mode.

We design a system platform called Phoenix Processor, in which we demonstrate the effectiveness of comprehensive standby power reduction techniques. These techniques include technology selection and power gating switch design methodology for ultra low voltage operations (Chapters III and IV, respectively). It also employs ultra low leakage SRAM design operating at ultra low voltage regimes (Chapter II), robust ultra low voltage ROM (Chapter V), and architecture optimizations with hardware compression support (Chapter II). All these techniques enables 35.4pW standby power and 226nW active power with approximately 100kHz performance at 0.5V. The average power consumption with a typical operation of  $10^5$  duty ratio is 37pW. The footprint of the system is less than  $1mm^2$  in industrial  $0.18\mu m$  CMOS technology, including 2kb SRAM, 640b ROM, 8b CPU, a watchdog timer, and a temperature sensor. The ultra low power consumption theoretically enables approximately 5 year lifetime with a single  $1mm^2$  battery, which make it as a viable option for cubic millimeter sensor systems. This work is a result from multiple collaborators. I principally led the efforts on system-level design including technology selection, power gating switches, SRAM arrays, ROM arrays, and top-level integration.

#### 1.4.2 Designing Ultra Low Power Analog Building Blocks

Along with digital components such as memory and CPU, it is also critical to design analog and mixed-signal modules with minimal power budgets since they often need to be integrated in cubic millimeter sensing systems for self-contained functionality. Such analog and mixed-signal functions include power conversion, analogto-digital conversion, radio communication, sensing and time checking. It is an increasingly challenging task to minimize power consumption in those blocks since the performance and robustness often degrade with reduced power budget more rapidly than digital components.

We focus on designing a ultra low power voltage reference (Chapter VI) as a key building block for such analog and mixed signal modules. The prototype design, named 2-Transistor voltage reference, shows ~  $19ppm/^{o}C$  of temperature insensitivity, 0.033%/V of supply voltage insensitivity, -67dB of Power Supply Rejection Ratio (PSRR), and ~ 2.2pW of power consumption at 0.5V. It has only two MOS-FETs and consume very small footprint of  $1350\mu m^2$  in  $0.13\mu m$  CMOS process. Power, area, line sensitivity, PSRR, and minimum functional voltage are dramatically improved and all the other metrics are compared favorable to the state-of-arts. We also investigate the effect of process variations on the performance of 2T voltage references and propose a digitally trimmable 2T voltage reference for mitigating process variations. We also demonstrate easy technology portability by implementing the same designs in three different CMOS technologies. Several variants of 2T voltage references are also proposed to tailor a specific needs such as different output voltages and temperature-dependent output voltages.

#### 1.4.3 Improving Performance, Delay Variability and Energy Efficiency

Back to the digital design domain, there are still challenges to address before we widely use a ultra low voltage design as a design practice for cubic millimeter sensing systems. These challenges include improving degraded performance, mitigating heightened variability and improving energy efficiency beyond simple voltage scaling. The low performance is acceptable for control purposes; However, higher performance is often preferred, particularly for the systems with real-time process constraints [77]. Additionally, if designers see a ultra low voltage operation as a performance constrained design, delay variability must be adequately addressed. It is also important to improve energy efficiency beyond the limit of conventional voltage scaling as a subset of cubic millimeter sensing systems often require a significantly large amount of computations like digital signal processing [101].

Therefore, we propose circuit and architecture techniques to mitigate those challenges and apply them to designing a Fast Fourier Transform (FFT) core (Chapters VII). Pipelining is a well-known method to improve performance or trade the gained performance for energy savings. However, less pipelining, 100-200 Fan-Outof-4 (FO4) delays per stage, is often preferred in ultra low voltage designs for two benefits [103, 36, 83]. First, less pipelining has less energy overhead from sequential elements and clock distributions. Also, long paths per stage help to reduce delay variability from random process and environmental variations through averaging effects. Contrary to these common practices, we propose to use aggressive pipelining to improve energy efficiency and performance simultaneously. This can be achieved since shorter cycle time from pipelining can reduce leakage energy consumption from idling gates in circuits. Furthermore, since leakage energy consumption was stopping energy-saving voltage scaling, this reduction of leakage energy consumption extends useful voltage scaling, resulting in switching energy savings as well. This process is different from trading a gained performance for energy savings; it actually sets a new limit of better energy efficiency in ultra low voltage regimes. We utilize this superpipelining for multipliers, serving delay-critical paths of the FFT core. It saves 18% energy consumption and improves performance by  $3.6 \times$  at the same  $V_{DD}$ , compared to a non-pipelined design. Architecture modifications are also proposed for reducing idling parts in the FFT core and increasing throughput, resulting in  $2.86 \times$  better energy efficiency and  $6.2 \times$  better throughput.

For mitigating delay variability, we use a latch-based design for delay-critical blocks (e.g. multipliers). It removes the hard boundaries of flip-flops and thus reestablish long paths through cycle borrowing capability, which average out process variations along the paths. Clock network design is also critical for circuit variability since skew and slew variability can cause hold time violations. However, clock buffers is less effective to reduce the interconnect delay due to the negligible metal resistance in ultra low voltage regimes. Also buffers contribute a significant amount of skew and slew variability from Process, Voltage and Temperature (PVT) variations. Therefore, we propose a clock network design using a greatly reduced number of clock buffers and matched interconnects such as H-Tree. This method reduces skew and slew variability by several orders of magnitude with no energy overhead. More general framework for designing clock network in ultra low voltage operation is also discussed (Chapter VIII).

The FFT core is demonstrated in 65nm CMOS technology, consuming the lowest energy consumption of 17.7nJ per 1024-pt complex FFT while operating at the remarkable performance of 30MHz at 0.27V. The energy efficiency is improved by at least  $4 \times$  from state-of-arts. Also the performance is improved by several orders of magnitude, compared to tens to hundreds of kHz of typical ultra low voltage designs. This project is a collaboration work; I am directly responsible for super-pipelining technique, latch-based design, clock network design, and top-level integration.

#### 1.4.4 Contribution Summary

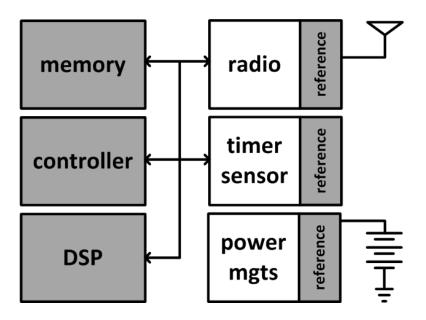

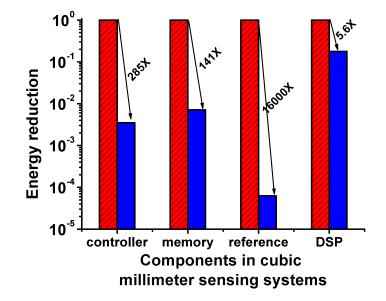

Along with mitigating variability and improving performance, the primary contribution of this work is to reduce energy consumption below the level that cubic millimeter systems require. Figure 1.4 shows the building blocks that directly benefits by this work: microcontroller, memory (SRAM and ROM), reference circuits, and Digital Signal Processing (DSP) unit. Reference circuits can be a key building block for several analog and mixed-signal modules such as timer, radio, sensors, and power conversion. The energy savings for each component are summarized in Figure 1.5. The large energy savings confirm the viability to build a cubic millimeter sensing system with a power source of the same scale while ensuring multi-year lifetime.

Figure 1.4: Components that can directly benefit from the design methodologies of this work in cubic millimeter sensing systems (in gray)

Figure 1.5: Energy efficiency improvement in the blocks of cubic millimeter sensing systems

### **1.5** Organization of this Work

The remainder of this thesis proposal is organized as follows. Chapter II focuses to present the the sensing platform, called Phoenix Processor, with ultra low power consumption both in standby and active mode. We emphasize one of the building block, ultra-low power custom SRAM array in this chapter. A brief discussion on micro-architecture design of Phoenix Processor is also presented. Chapter III, Chapter IV, and Chapter V in detail discuss three different standby strategies, namely technology selection, power gating switch design, and robust ROM array design, all employed in Phoenix Processor. After the discussions on Phoenix Processor, Chapter VI introduces a ultra low power voltage reference design as a key analog and mixed signal building block. We first focus on the basic topology of the proposed design. Then we discuss the impact of process variations, trimmable version for mitigating variability, technology portability and several variants of the proposed voltage reference. Finally, in Chapter VII, we introduce circuit and architecture technique to overcome other remaining issues of ultra low voltage designs, namely degraded performance, saturated energy efficiency, and heightened delay variability. A FFT core in 65nm is presented as an test vehicle to demonstrate the techniques. In Chapter VIII, we in detail discuss about robust clock network design, used in the FFT core design. Finally, Chapter IX concludes this work.

## CHAPTER II

# Phoenix Processor: 35pW Standby and 226nW Active Power Sensor Platform

## 2.1 Motivation and Previous Work

The prevalence of mobile computing has helped define a vision of complex computational resources in cubic centimeter scale [104, 72] and smaller scale. As the volumes of computing resources approach one cubic millimeter, active monitoring and actuation can be used to enrich a wide range of applications. Cubic millimeter computing will be particularly important in implantable medical devices, where reducing device volume helps minimize implant damage to the body. The diagnosis and treatment of Glaucoma, for example, requires periodic measurements of pressure in the eye (intraocular pressure). Intra-ocular pressure is currently monitored directly by a doctor, requiring frequent trips to the doctor's office to ensure sufficient temporal resolution [82]. An intra-ocular pressure sensor with a MEMS pressure sensor, microprocessor, memory, radio and power source small enough to be implanted in the eye would reduce both cost and time investment and would increase the temporal resolution of pressure measurements.

Although MEMS and circuit components easily meet the volume constraints of intra-ocular pressure sensing and other cubic millimeter computing applications, batteries and energy scavenging power sources cannot be easily miniaturized while also serving the power demands of the MEMS and circuit components. Minimizing the power demands of each component is therefore one of the central challenges in designing a cubic millimeter computing system. Consider a system with a thin film zinc/silver oxide battery with a capacity of  $100\mu Ah/cm^2$  and output voltage of 1.55V [63]. If the battery size is restricted to  $1mm^2$ , the average system current must be only 114pA (for power consumption of 177pW) to guarantee one year of battery life.

Early work proved that operation at extremely low voltage was possible [102] and later work demonstrated full subthreshold microprocessors operating at record low energy consumption [37, 116, 57]. Recent research has also shown that memory can be redesigned to operate robustly at low voltage [20, 16, 114]. However, the 177pW power budget is still several orders of magnitude less than most energy efficient microprocessor designs consume [36, 57, 101]. Therefore it is paramount to reduce the power of such systems.

In particular standby power consumption need to be minimized since a typical wireless sensing system may spend the majority of its lifetime in standby mode. For example, a typical wireless sensor data logger might take sensor measurements once every 10 minutes. Assuming a 100ms active period, the sensor spends  $6000 \times$  more time in standby mode than active mode. This disparity is of particular importance in low voltage systems, where leakage energy is comparable to dynamic energy in magnitude [113]. For example, the low voltage processor in [37] consumes only  $5 \times$  more power in active mode than it does in a clock gated standby mode. Total energy consumed in standby mode would exceed total energy consumed in active mode by  $1200 \times$  if this low voltage processor were used in the aforementioned wireless sensing system.

## 2.2 Contribution

Given the importance of standby mode power, we focus in this work on the development of an ultra low energy sensor processor designed for deep standby operation, called the Phoenix Processor [83]. The Phoenix Processor is a complete digital system for cubic millimeter computing that includes an 8-bit CPU, data and instruction memories, a watchdog timer, and a simple temperature sensor. In addition to aggressive voltage scaling, the Phoenix Processor leverages a comprehensive sleep strategy including system-level optimization for low voltage operation, a unique power gating approach, a ultra low leakage custom SRAM, a robust low  $V_{DD}$  ROM, an 8bit CPU with compact instruction set, and data memory compression.

My main contribution in this project includes the system-level optimization including technology selection, a unique power gating approach, a ultra low leakage custom SRAM and a robust low  $V_{DD}$  ROM along with a system integration. The 8 bit CPU design with optimized Instruction Set Architecture (ISA) and hardware compression support, the watchdog timer and the temperature sensor are primarily designed by my co-workers. Measurements of a  $0.18\mu m$  test chip reveal that Phoenix consumes 226nW in active mode and only 35.4pW in sleep mode. Assuming  $10^4 \ 10^5$ duty ratio, the average power is 58-37pW, which is below the required power budget for cubic millimeter scale sensing system.

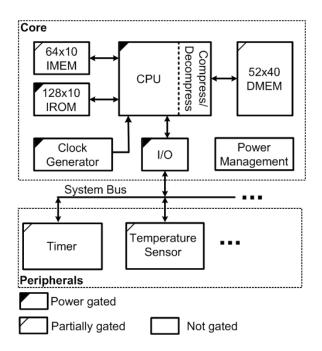

### 2.3 System Overview

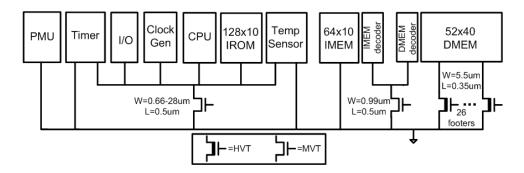

As shown in Figure 2.1, the Phoenix Processor is a modular system with a core unit consisting of an 8-bit CPU, a 52x40-bit data RAM (DMEM), a 64x10-bit instruction RAM (IMEM), a 64x10-bit Instruction ROM (IROM) and a Power Management Unit (PMU). The core serves as a parent to peripheral devices, including a watchdog timer and a temperature sensor. The core and peripheral devices communicate over a

Figure 2.1: The Phoenix Processor.

system bus using a simple asynchronous protocol. The Input and Output (I/O) controller addresses up to 8 peripherals on the system bus for sensing systems requiring additional peripherals.

In typical operating conditions, the Phoenix Processor spends an extended period of time in standby mode (e.g., 10 minutes) and wakes up in response to an exception raised by the watchdog timer (a 0.9pW current-starved oscillator). Once awake, the Phoenix Processor polls the temperature sensor and runs a short routine to process and store the measurement. After completing the data processing routine, Phoenix returns to standby mode.

The power consumption in active mode is dominated by components with high switching activity, such as the CPU. To minimize this source of power consumption we scale voltage aggressively to 0.5V, a sub-threshold voltage (for high- $V_{th}$  devices) or near-threshold voltage (for medium- $V_{th}$  devices) in the target technology. The challenges of low voltage digital design have been covered extensively in recent literature [37, 116, 102] and will not be the focus of this work.

Instead, we place emphasis on accommodations made for standby mode operation. The Phoenix Processor was designed at the device, circuit and architecture levels with the primary goal of standby power minimization. In subsequent sections, we discuss each of the key components of this comprehensive standby mode strategy. We begin in Section 2.4 by discussing the design of "retentive gates," which are the gates that remain awake during standby mode. These include the PMU, timer, and portions of IMEM and DMEM. Without proper attention, retentive gates dominate standby mode power consumption. In Section 2.5 we discuss a unique power gating approach for power minimization in non-retentive gates (i.e., gates that sleep during standby mode). During standby mode, between 65% and 87% of all transistors are power gated, so efficient power gating is critical. The CPU architecture also plays an important role in determining standby mode power. We discuss the design of the CPU in Section 2.6 and pay particular attention to the ISA definition since this determines the footprint of IMEM, a significant source of leakage during standby mode. The CPU includes software and hardware support for DMEM compression, which is discussed in Section 2.7. As we will show using device measurements, the power consumption of retentive memory cells dominates the standby mode power consumption, so we devote Section 2.8 to discussing a custom SRAM cell that achieves ultra low leakage at a low operating voltage.

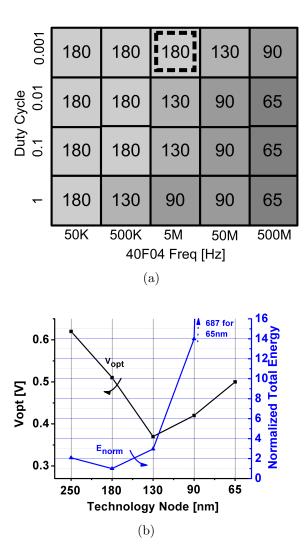

# 2.4 System-level Optimization including Technology Selection

Perhaps most important to minimizing power consumption in standby mode is technology selection. Despite its importance to both power and performance, there has been little investigation of technology selection for low voltage circuits. The requirements of sub-threshold and near-threshold circuits are different than those of normal super-threshold circuits, and the optimal technology is therefore different. The required performance is much relaxed in typical low voltage sensing applications. Consequently, older technologies can easily meet performance requirements. Additionally, leakage becomes more important in low voltage operation than in superthreshold operation, making older technologies with high- $V_{th}$  devices attractive. Near the energy-optimal supply voltage [113], leakage energy in active mode is comparable to switching energy. Furthermore, the long standby time observed in many sensor applications makes cumulative standby leakage energy significant as we observed earlier in this work. Advanced technology nodes have also been optimized exclusively for super-threshold operation. Consequently, inverse subthreshold swing degradation in scaled super-threshold devices leads to a reduction in noise margins and sub-optimal power and performance, as shown in [36]. The ideal technology would simultaneously offer small feature sizes and devices with ultra low leakage. Since no such technology was available for use in academic research, we investigated standard CMOS technologies from  $0.25\mu m$  to 65nm using the method in [84] to determine the energy-optimal technology.

The optimization has been performed to minimize total energy consumption. We identify 5 high-level factors that affect the total energy of the system: technology, the size of power gating switch, supply voltage, duty cycle (defined as active time to total time ratio), and the ratio of memory to logic area. The memory to logic area ratio and duty cycle are determined primarily by application requirements while technology, the size of power gating switch, and supply voltage are chosen to minimize total energy consumption.

In order to find the ratio of memory to logic area, we need to estimate DMEM and IMEM size for applications. We examine periodic sensor data logging as a typical operation. We choose 512 words of DMEM since it will take approximately one year to fill the 512 words if one word of data is stored on daily basis. The IMEM size is set relatively smaller at 64B since it is supplemented with 128B IROM. Adding more IROM can be done with negligible increase in standby power. However the size of DMEM and IMEM needs to be changed for different applications. Based on the DMEM and IMEM size, we estimate the area ratio of memory to logic as 1, which is backed by the actual die photo in Figure 2.13. Duty cycle is assumed to be 0.001.

With the chosen area ratio of memory to logic and the duty cycle, we optimize the total energy consumption by sweeping technology, the size of power gating switch, and supply voltage based on the optimization framework in Chapter III. Five industrial CMOS technologies from 65nm to  $0.25\mu m$  are considered. Supply voltage and the size of the power gating switch are selected within the range allowed by each technology. The Phoenix Processor is abstracted as a large collection of inverter chains with different activity ratios. The activity ratio for SRAM modules (DMEM and IMEM) is assumed to be 0.02 while that for CMOS logic (CPU, IROM) is set  $10 \times$  larger at 0.2. We include high- $V_{th}$  devices in the optimization process since they can be used in the SRAM bitcell for leakage reduction. High- $V_{th}$  I/O devices are also considered as a viable option for building bitcells.

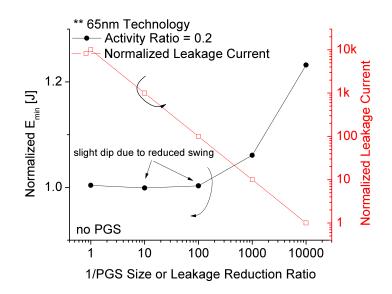

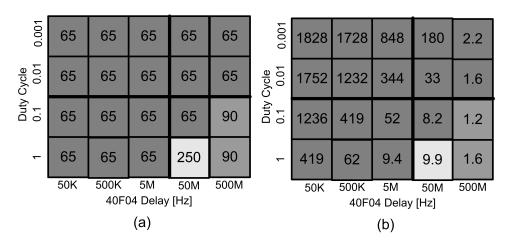

The result of the optimization is shown in Figure 2.2. The matrix shows the energy optimal technology at the given performance and duty cycle requirement of each application. With the target duty cycle of 0.001, we have three different optimal technologies for different performance requirements. Since the Phoenix Processor has a relaxed performance requirement and higher performance causes more energy consumption,  $0.18\mu m$  is selected as the energy optimal technology.

For the highlighted block whose duty cycle is 0.001 and performance is 5MHz (frequency of 40 FO4 delay), the optimal supply voltage and energy is plotted in the Figure 2.2. Old technologies are favored since they have lower leakage energy. The reason why  $0.18\mu m$  technology gives lower energy consumption than  $0.25\mu m$  is that the particular  $0.18\mu m$  that we investigated has a higher- $V_{th}$  I/O device than

Figure 2.2: (a) Energy optimal technology matrix (b) Optimal  $V_{DD}$  and energy over technologies

the  $0.25\mu m$  technology. The  $0.18\mu m$  technology includes a thin-oxide medium- $V_{th}$  device with  $V_{th} = 0.5$ V and a thick-oxide I/O device with  $V_{th} = 0.7$ V. All retentive gates are implemented using the high- $V_{th}$  devices, which consume several orders of magnitude less leakage power per unit of gate width than the medium- $V_{th}$  devices. If the  $0.25\mu m$  technology offered a comparable high- $V_{th}$  device, it could be the optimum choice unless the area overhead associated is intolerable. Note that we do not use high- $V_{th}$  devices in non-retentive gates since the minimum dimension is larger than that of the thin-oxide device, which gives both area and active energy penalties. The optimum supply voltage estimated is 0.5V. The size of the power gating switch is determined proportionally to the relative size of actual modules to the inverter chains used in the optimization process.

In addition to the selection of an older technology, stack-forcing is used to reduce leakage power further. Leakage reduction due to the stack effect has been shown in previous work to be effective [68]. In our selected technology, stacking two transistors gives  $2 \times$  leakage reduction.

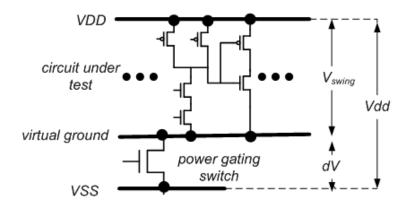

### 2.5 Power Gating Under Relaxed Performance Constraints

A power gating switch, as shown again in Figure 2.3, is often used in low power circuits to minimize leakage in non-retentive circuit blocks during standby modes. At normal super-threshold operating voltages (e.g., > 1V in 45nm and 65nm designs), a high- $V_{th}$  device is typically used as a power gating switch since it delivers comparable on-current to the nominal device with exponentially smaller off-current. Additionally, wide power gating switches are typically used to minimize the performance penalty of power gating.

For cubic millimeter computing applications with modest performance requirements, minimizing standby power is the most important goal. In such applications, performance can be sacrificed for lower leakage, which is in stark contrast to the typ-

Figure 2.3: A typical power gating switch.

ical approach to power gating. In the Phoenix Processor, we leverage these modest performance requirements with a unique power gating approach.

Our power gating approach relies on a medium- $V_{th}$  power switch rather than a high- $V_{th}$  switch as in the typical approach. Since the on-current of the high- $V_{th}$  device is exponentially smaller than that of the medium- $V_{th}$  device at low voltage, a high- $V_{th}$  device must be sized up 1000× as compared to a medium- $V_{th}$  device to meet the current demands of the primary circuit, which is implemented using medium- $V_{th}$ devices. The area overhead as well as the power overhead of charging/discharging such a large switch is avoided by using a medium- $V_{th}$  power switch.

In addition to using medium- $V_{th}$  power switches, the strength of our power gating switch compared to the circuit under test is smaller than that of the typical power gating approach. A stronger power gating switch minimizes the performance penalty of power gating at the expense of additional leakage during standby mode. Given the modest performance demands for the Phoenix Processor, we choose to reduce standby mode leakage considerably by selecting a very weak power gating switch [84].

In the Phoenix Processor, the medium- $V_{th}$  power switch is only  $0.66\mu m$ , which is 0.01% of total effective Negative Channel Field Effect Transistor (NFET) width and  $3 \times$  larger than the minimum width in the target technology. We increase the length from  $0.18\mu$ m to  $0.50\mu$ m to improve inverse subthreshold slope and consequently

Figure 2.4: Footer allocation in the Phoenix Processor.

increase the on-current to off-current ratio. The  $0.66\mu m$  power gating switch is connected to the CPU and several other logic blocks as shown in Figure 2.4. Simulations with a model of the CPU indicate that the virtual ground rail bounces by a maximum of 100mV, which is sufficient to guarantee correct logic operation. The non-retentive parts of IMEM and DMEM, such as decoders and output buffers, are connected to a separate power gating switch since the robustness of low voltage memory may be compromised by a voltage drop across the power gating switch. The measured energy and performance implications of our proposed power gating strategy will be discussed in Section 2.10.

# 2.6 CPU and Instruction Set Design for Standby Mode

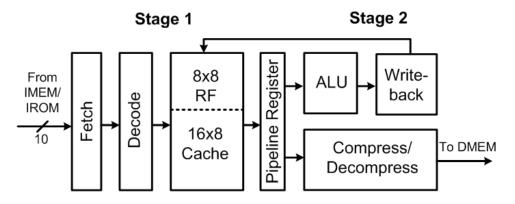

In accordance with the conclusions of previous studies of subthreshold processor architectures [69], we have selected a simple CPU architecture with 2-stage pipeline, 8-bit data width, and 10-bit instruction width to reduce active mode power and standby mode power. The instruction set includes support for basic arithmetic computation in typical sensor logging applications. As shown in Figure 2.5, the first pipeline stage consists of instruction fetch and decode as well as a scratch memory with an 8-entry register file and 16-entry cache. The second pipeline stage includes a simple ALU, write-back logic, and a memory interface unit that compresses (decompresses) outgoing (incoming) memory traffic. The ALU includes hardware for

Figure 2.5: CPU diagram.

addition, subtraction, and shifting. The CPU has been designed to minimize energy in both active and standby modes, as shown in the remainder of this section.

Since the computational demands of cubic millimeter computing applications are typically modest, the CPU was simplified to support a minimum set of operations. Such simplicity reduces decode complexity and eliminates unnecessary switching activity, thus reducing active mode power. Furthermore, elimination of complex operations like multiplication eliminates large, leaky circuit blocks. Since leakage energy can be >30% of total energy in active mode for low voltage circuits [113], the resulting active mode power savings are significant.

ISA optimization also plays an important role in minimizing power consumption in standby mode. Since the contents of IMEM must be retained in standby mode, it is important to minimize the instruction width. The leakage penalty of instruction memory can alternatively be eliminated by using non-volatile memory, but this requires costly processing steps. The custom ISA for the Phoenix Processor was compressed to an instruction width of only 10 bits by selecting a minimum set of 18 instructions.

| Class        | Members                     | Addressing Mode |

|--------------|-----------------------------|-----------------|

| Arithmetic   | ADD, ADDI, SUB, MOVE, SHR   | explicit        |